# **Brigham Young University BYU Scholars Archive**

Theses and Dissertations

2007-03-08

# Circuit and Modeling Solutions for High-Speed Chip-to-Chip Communication

**Timothy Mowry Hollis** Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **BYU ScholarsArchive Citation**

Hollis, Timothy Mowry, "Circuit and Modeling Solutions for High-Speed Chip-to-Chip Communication" (2007). Theses and Dissertations. 1067.

https://scholarsarchive.byu.edu/etd/1067

This Dissertation is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

# CIRCUIT AND MODELING SOLUTIONS FOR HIGH-SPEED CHIP-TO-CHIP COMMUNICATION

by

Timothy M. Hollis

A dissertation submitted to the faculty of  $$\operatorname{Brigham}$$  Young University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Department of Electrical and Computer Engineering

Brigham Young University

Copyright © 2007 Timothy M. Hollis All Rights Reserved

#### BRIGHAM YOUNG UNIVERSITY

#### GRADUATE COMMITTEE APPROVAL

of a dissertation submitted by

Timothy M. Hollis

This dissertation has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

| Date | David J. Comer, Chair |

|------|-----------------------|

| Date | Donald T. Comer       |

| Date | Michael A. Jensen     |

| Date | Michael D. Rice       |

| Date | Karl F. Warnick       |

#### BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the dissertation of Timothy M. Hollis in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

| Date                        | David J. Comer<br>Chair, Graduate Committee                                 |  |

|-----------------------------|-----------------------------------------------------------------------------|--|

|                             |                                                                             |  |

|                             |                                                                             |  |

| Accepted for the Department |                                                                             |  |

|                             | Michael J. Wirthlin<br>Graduate Coordinator                                 |  |

| Accepted for the College    |                                                                             |  |

|                             | Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology |  |

#### ABSTRACT

# CIRCUIT AND MODELING SOLUTIONS FOR HIGH-SPEED CHIP-TO-CHIP COMMUNICATION

Timothy M. Hollis

Electrical and Computer Engineering

Doctor of Philosophy

This dissertation presents methods for modeling and mitigating voltage noise and timing jitter across high-speed chip-to-chip interconnects. Channel equalization and associated tuning schemes have been developed to target the distinct characteristics and signal degradation exhibited in the clock and data signals of multi-Gigabit/second digital communication links. Multiple methods for generating realistically degraded signals for the purpose of simulation are also presented and used to verify the proposed equalization and filtering topologies.

Specifically, a new technique for modeling high-speed jittery clocks in the frequency domain is presented and shown to reduce transient simulation time and memory requirements, while simultaneously improving the timing resolution and accuracy of the simulation by minimizing the dependence on the transient simulation time-step. The technique is further developed to provide unprecedented control over the timing characteristics of the generated signals, and is then extended to the generation of random data signals with definable jitter statistics. Through these techniques,

realistic clock and data waveforms are constructible, providing for the visualization of the combined effects of voltage and timing degradation, while at the same time tracking the phase relationship between the clock and data signals as they pass across their respective channels and through the receiving circuitry of the communication link.

New methods for the automated tuning of second-order continuous-time channel equalizers are proposed based on the simulated or measured single pulse and double pulse responses of the transmission channel. Using only one degree of freedom, the methods target the reduction of inter-symbol interference (ISI) as identified in the single and double pulses. Through tuning either the circuit quality factor (Q), the peaking frequency, or the frequency zero, the methods are shown to adapt to a variety of channel lengths and datarates from the same original equalizer transfer function, implying a good degree of generality, while offering a simple, yet effective, method for ISI reduction.

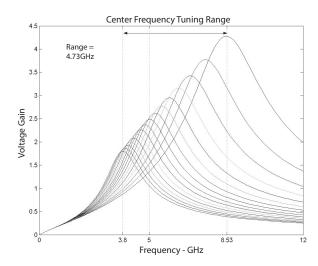

Finally, the design of an active 5 Gigahertz (GHz) bandpass filter, employed for high-speed clock conditioning, is presented and shown to address both random and deterministic components of the clock signal degradation. The bandpass transfer function is achieved through a combination of AC coupling and a resonant LC tank consisting of on-chip interleaved spiral inductors and a tunable capacitor array. Through adjusting the load capacitance in parallel with the inductors, the center frequency of the filter is tunable over a range of nearly 5GHz. The design targets a supply voltage of 1.2 volts and draws approximately 5.7 milliamps of current.

#### ACKNOWLEDGMENTS

I would like to start by thanking my wife Alisha, who has stood by me and supported me not just through the process of obtaining the PhD, but through nearly fifteen years of schooling. Even when, after completing a degree in Psychology, I made a U-turn and decided to pursue electronics and engineering (the second best decision of my life following marrying her), she was right behind, encouraging me, willing to make any sacrifice to help me succeed. I would also like to thank my children: Jeremiah, Emily, Samuel, Evelyn, and Isaac who have been very patient with me as I have tried to balance school, work, and being an involved dad. I would like to thank my parents and my sisters for their encouragement and would especially like to acknowledge my grandfather, an engineer himself, who convinced me that I would not be satisfied with anything less than the doctoral degree.

I would like to thank several professors from Brigham Young University, with particular thanks going to Dr. David Comer who has taught me more than just about engineering and carrying out research, but also about being a man of integrity. I have greatly appreciated his trust in me, which he has shown by always encouraging me to pursue inspiration. I wish to acknowledge Dr. Don Comer also for his mentoring. Dr. Comer frequently demonstrated how to think "outside the box" and in doing so often helped me identify unrealized nuances of my work. To the remaining members of my advisory committee, I am also grateful. To Dr Jensen I am grateful for the financial support he provided through the graduate program, which not only relieved my concerns over paying tuition, but also made it possible for me to present my research at international conference events. To Dr. Rice for his insights on particular areas of my study and guiding me to resources that broadened

my understanding of the problem. And finally to Dr. Warnick who, in his humble way, was often able to show me a more mature mathematical approach to what I was working on. I always left his office with a deeper understanding and appreciation for the fundamentals.

I would like to thank two professors from the University of Utah, Dr. Neil Cotter and Dr. Reid Harrison. Dr. Cotter took personal time to meet with me and guide me through some of the most important decisions I had to make as I neared the end of my undergraduate career. In a similar way, Dr Harrison gave me advice, without which I may not have had the opportunity at BYU that I did.

I would like to thank Dan Spangler, who while a leader of the Micron Foundation, spent his valuable time sharing with me insights from the technology industry and also providing advice that I felt very confident following. Within Micron, I would also like to specifically thank Brent Keeth for allowing me to build upon the work I began in school and for challenging me in ways that eventually lead to new levels of development in my personal research. In addition to Dan and Brent, I want to thank both Micron Technology, Inc. and the Micron Foundation for financial support and internship opportunities that have directly and indirectly contributed to this work. I have often been amazed by the level of personal encouragement that I have received from several sources at Micron.

I would like to thank the Intel Corporation also for financial support and an internship that served to focus my direction and the scope of my research very early in the process. I would like to specifically acknowledge Bryan Casper and Frank O'Mahony for their mentoring during and following my internship with the High Speed Signaling group at Intel. Bryan opened my eyes to new perspectives on jitter analysis while Frank took the time to pass along helpful analog circuit design techniques.

Finally, I would like to publically thank my Heavenly Father for sending inspiration in my times of need.

## **Table of Contents**

| Li | st of                  | Tables                   | S                                             | xxi  |

|----|------------------------|--------------------------|-----------------------------------------------|------|

| Li | $\operatorname{st}$ of | Figure                   | es x                                          | xvii |

| 1  | Intr                   | $\operatorname{roducti}$ | ion                                           | 1    |

| 2  | Hig                    | h-Spee                   | ed Interconnects - Topologies and Limitations | 7    |

|    | 2.1                    | Comm                     | non Interconnect Topologies                   | 7    |

|    | 2.2                    | Signal                   | Degradation                                   | 10   |

|    |                        | 2.2.1                    | Voltage Noise                                 | 12   |

|    |                        | 2.2.2                    | Timing Noise - Jitter                         | 20   |

|    | 2.3                    | Impac                    | t of Noise on Link Performance                | 32   |

| 3  | Cur                    | rent N                   | Modeling and Simulation Practices             | 37   |

|    | 3.1                    | Model                    | ing Efficiency versus Precision               | 37   |

|    |                        | 3.1.1                    | Transistor-level Analysis                     | 38   |

|    |                        | 3.1.2                    | System-level Simulation                       | 43   |

| 4  | Rea                    | distic S                 | Signal Generation for System Verification     | 55   |

|    | 4.1                    | Fourie                   | er-Based Waveform Generation                  | 55   |

|    |                        | 4.1.1                    | Fourier-based Clock Signal Derivation         | 56   |

|    |                        | 4.1.2                    | Enhanced Clock Simulation Efficiency          | 61   |

|    |                        | 4.1.3                    | Unconstrained Waveform Generation             | 69   |

|    |                        | 4.1.4                    | Fourier-based Data Signal Generation          | 69   |

|    |                        | 4.1.5                    | Signal Generation Summary                     | 71   |

|    |                        | 4.1.6                    | Verification                                  | 73   |

|   | 4.2 | Jitter  | Injection                              | 74  |

|---|-----|---------|----------------------------------------|-----|

|   |     | 4.2.1   | Additional Applications                | 75  |

|   |     | 4.2.2   | Limitations                            | 78  |

|   | 4.3 | Altern  | native Signal Generation Algorithms    | 79  |

| 5 | Mit | igating | g Noise and Distortion in the Channel  | 83  |

|   | 5.1 | Filteri | ing Noise                              | 84  |

|   |     | 5.1.1   | Matched Filtering                      | 85  |

|   | 5.2 | Minim   | nizing Distortion                      | 89  |

|   |     | 5.2.1   | Transmit Pulse Shaping                 | 89  |

|   |     | 5.2.2   | Channel Equalization                   | 90  |

|   |     | 5.2.3   | Discrete-Time Equalization             | 95  |

|   |     | 5.2.4   | Continuous-Time Equalization           | 99  |

|   |     | 5.2.5   | Disruptive Equalizer Technologies      | 104 |

|   |     | 5.2.6   | Future Equalization                    | 105 |

| 6 | Con | ntinuoı | us-Time Equalizer Calibration          | 107 |

|   | 6.1 | The L   | inear Equalizer                        | 108 |

|   |     | 6.1.1   | Equalizer Coefficient Placement        | 110 |

|   |     | 6.1.2   | Equalizer Coefficient Tuning           | 111 |

|   |     | 6.1.3   | Additional Simulation Results          | 134 |

|   | 6.2 | Perfor  | mance Summary                          | 134 |

|   |     | 6.2.1   | Possible Circuit Implementation        | 141 |

| 7 | Hig | h-Spe   | ed Clock Filter                        | 145 |

|   | 7.1 | Revie   | w of Clock Jitter                      | 148 |

|   |     | 7.1.1   | Suppression of Random Jitter           | 148 |

|   |     | 7.1.2   | Suppression of DCD                     | 151 |

|   |     | 7.1.3   | Periodic and Sinusoidal Jitter         | 153 |

|   | 7.2 | Existi  | ng Solutions for Reducing Clock Jitter | 156 |

|   | 7.3 | Design  | n of the Clock Filter                  | 159 |

|   | 7.4 | Bandr   | pass Clock Equalizer Tuning Schemes    | 164 |

|    |        | 7.4.1   | Existing Tuning Solutions      | 165 |

|----|--------|---------|--------------------------------|-----|

|    |        | 7.4.2   | Proposed Filter Tuning Schemes | 167 |

|    | 7.5    | Perfor  | mance of the Clock Filter      | 172 |

| 8  | Cor    | nclusio | n                              | 177 |

|    | 8.1    | Summ    | ary of Contributions           | 177 |

|    | 8.2    | Areas   | of Future Interest             | 180 |

| Bi | ibliog | graphy  |                                | 197 |

## List of Tables

| 4.1 | Simulation Time and Memory Requirements                           | 64  |

|-----|-------------------------------------------------------------------|-----|

| 6.1 | Equalizer Coefficient Values                                      | 129 |

| 6.2 | Comparison of Equalizer Performance                               | 144 |

| 7.1 | Final Filter Component Values                                     | 160 |

| 7.2 | Simulated Filter Characteristics and Performance                  | 175 |

| 7.3 | Comparison of Filter Performance with Previously Published Work . | 176 |

# List of Figures

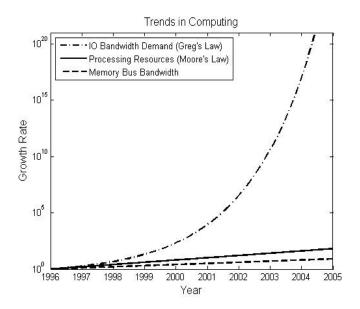

| 1.1  | Trends in computing speed supply and demand                                                                                                                                                                                                            | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

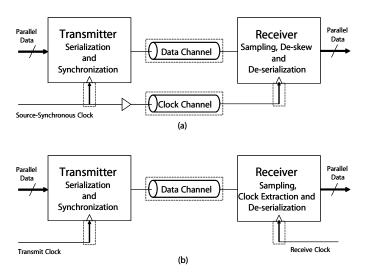

| 2.1  | Simplified diagrams of source-synchronous (top) and clock-data-recovery (bottom) interconnect topologies                                                                                                                                               | 8  |

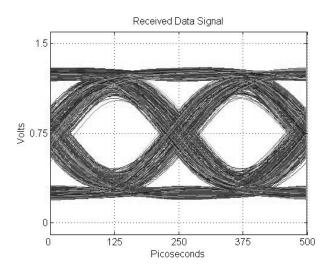

| 2.2  | Example data eye diagram                                                                                                                                                                                                                               | 11 |

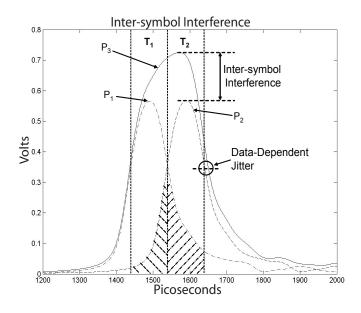

| 2.3  | Illustration of the impact of ISI on signal amplitude and transition timing                                                                                                                                                                            | 17 |

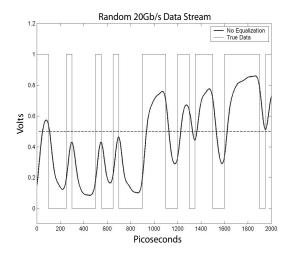

| 2.4  | Comparison of transmitted data and the corresponding unequalized received data                                                                                                                                                                         | 19 |

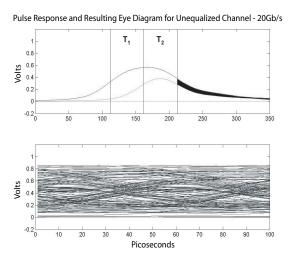

| 2.5  | The upper window presents the 20 Gb/s single and double pulse responses of the six inch FR4 channel with no equalization. The lower window presents the resulting 20 Gb/s eye diagram. The shaded area in the upper window represents accumulating ISI | 20 |

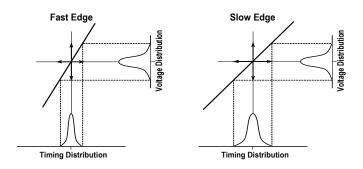

| 2.6  | Illustration of the translation of random noise to random jitter through the slew-rate of the signal transition                                                                                                                                        | 21 |

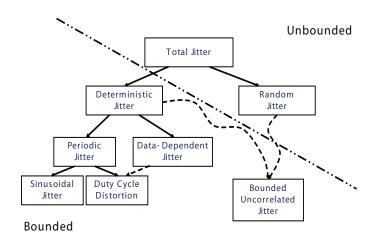

| 2.7  | Decomposition of jitter                                                                                                                                                                                                                                | 22 |

| 2.8  | Definition of the jitter impulse response                                                                                                                                                                                                              | 25 |

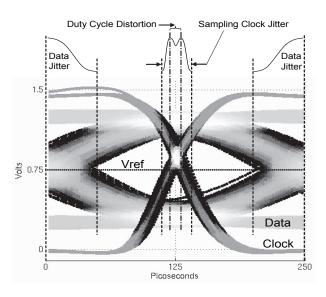

| 2.9  | Eye diagram illustrating the effects of both clock and data jitter on timing margin. Duty cycle distortion produces the bi-modal sampling clock distribution                                                                                           | 26 |

| 2.10 | Illustration of how the addition of DC offset to a perfectly symmetric, finite rise/fall time, square wave generates duty cycle error                                                                                                                  | 27 |

| 2.11 | DCD accumulation across lowpass channels                                                                                                                                                                                                               | 28 |

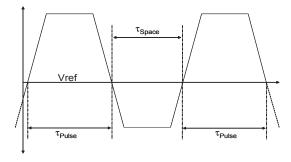

| 2.12 | Waveform used in the derivation of the Fourier series representing a clock with DCD                                                                                                                                                                    | 29 |

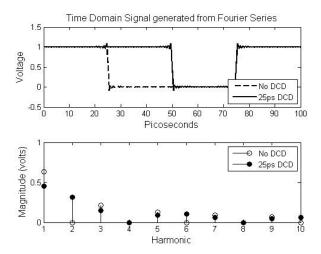

| 2.13 | The upper window presents an ideal clock waveform compared with a clock exhibiting 25 ps of DCD as generated through the parameterized Fourier series just derived. The lower window presents the resulting variation in the 10 GHz fundamental and the first nine higher order harmonics, illustrating the high frequency nature of DCD                                    | 31 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Detailed block diagram of the typical meso-synchronous link                                                                                                                                                                                                                                                                                                                 | 33 |

| 2.15 | Diagram identifying various forms of signal degradation                                                                                                                                                                                                                                                                                                                     | 34 |

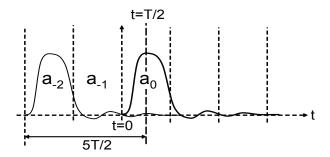

| 3.1  | Received pulse train illustrating the contribution of symbols $a_n$ to the signal amplitude at time $t$                                                                                                                                                                                                                                                                     | 44 |

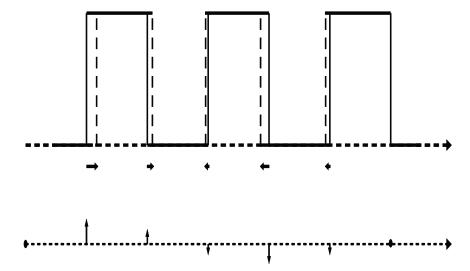

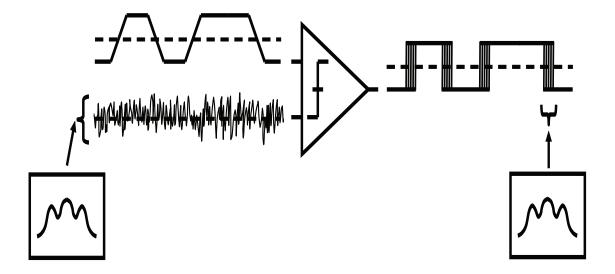

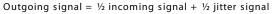

| 3.2  | A known method for generating signals with jittery edges                                                                                                                                                                                                                                                                                                                    | 48 |

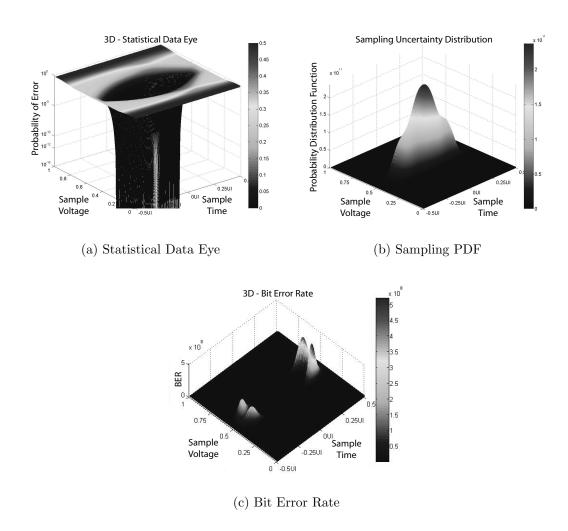

| 3.3  | Illustration of the BER eye derivation. (a) Probabilistic data eye generated from ISI pdf at 1 ps intervals. (b) Sampling uncertainty distribution generated from the products of independent voltage and timing noise distributions. (c) BER derived from the product of the values from b and c                                                                           | 51 |

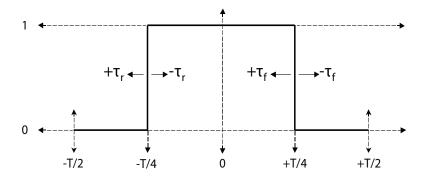

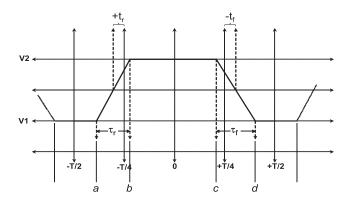

| 4.1  | Signal model from which the coefficients of the generic Fourier series are derived                                                                                                                                                                                                                                                                                          | 56 |

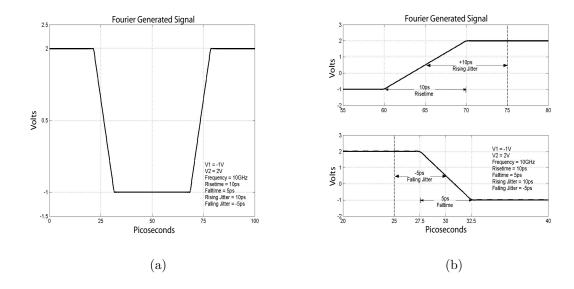

| 4.2  | (a) One cycle of the generated clock waveform. (b) Magnified rising and falling edges of the generated clock                                                                                                                                                                                                                                                                | 59 |

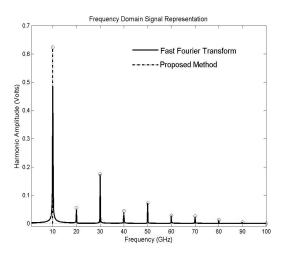

| 4.3  | Comparison of the signal frequency response taken directly from the Fourier coefficients computed in the proposed signal generation process with those calculated in PSpice through the FFT                                                                                                                                                                                 | 62 |

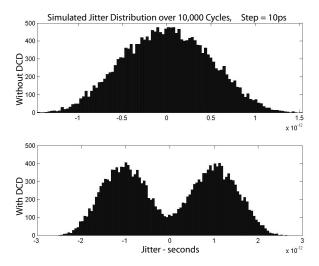

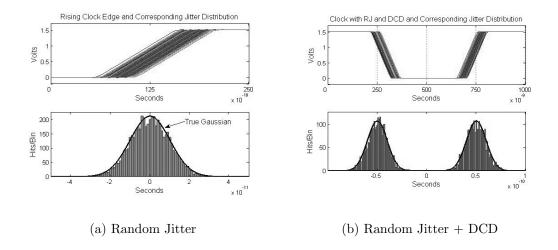

| 4.4  | Simulation of random and deterministic jitter                                                                                                                                                                                                                                                                                                                               | 66 |

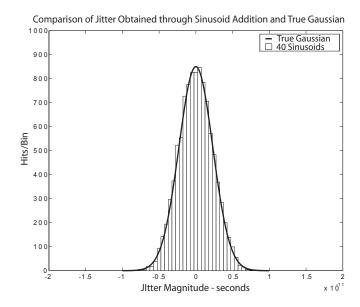

| 4.5  | Simulated jitter (40 sinusoids) compared with a true Gaussian pdf                                                                                                                                                                                                                                                                                                           | 67 |

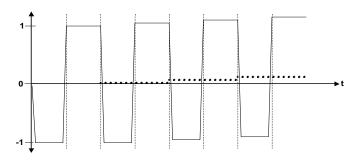

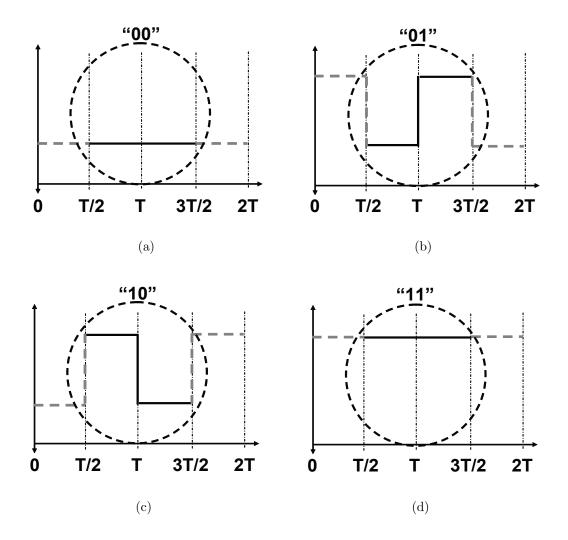

| 4.6  | Four data symbols used to represent binary NRZ signaling                                                                                                                                                                                                                                                                                                                    | 70 |

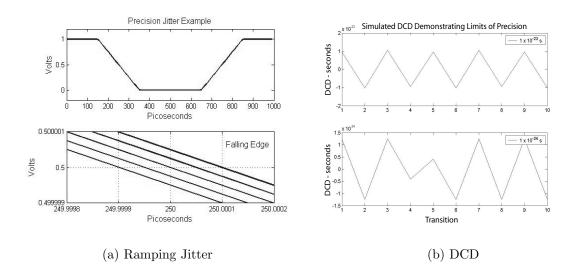

| 4.7  | Demonstration of the time-domain precision of the proposed waveform generation. (a) The upper window shows a 1 GHz clock waveform generated through the proposed method. The lower window presents an incremental jitter of 0.5 fs generated with a time step of 10 ps. (b) Demonstration of DCD successfully simulated down to $1\times10^{-23}$ with a time step of 50 fs | 72 |

| 4.8  | Comparison of generated jitter and theoretical jitter distributions                                                                                                                                                                                                                                                                                                         | 73 |

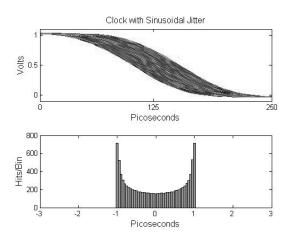

| 4.9  | Clock jitter distribution indicating the presence of sinusoidal jitter                                                                                                                                                                                                                                                                                                      | 74 |

| 4.10 | Method for injecting jitter into an existing signal                                                                                                                                                                                                                                                                                                                         | 75 |

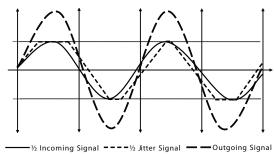

| 4.11 | Signal derived from Fourier components while the frequency is modulated from 1 MHz to 20 MHz                                                                                                                                                                                   | 76  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

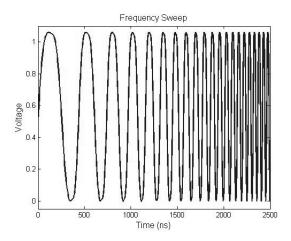

| 4.12 | Periodic clock and random data signals exhibiting both random jitter and sinusoidal jitter components as generated by the proposed algorithm with associated time-domain extracted jitter and associated histograms. (a) Jittery clock signal. (b) Jittery random data signal. | 82  |

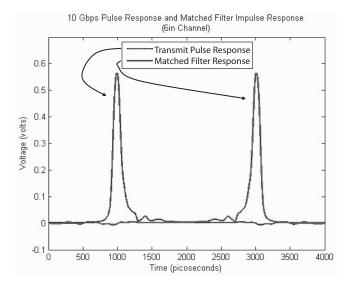

| 5.1  | The six inch channel - 10 Gb/s pulse response and corresponding, artificially delayed, matched-filter impulse response                                                                                                                                                         | 86  |

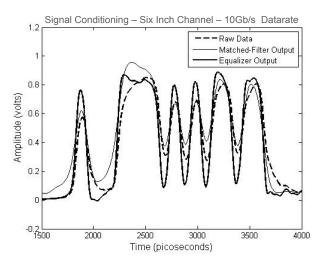

| 5.2  | Comparison of raw, match-filtered , and equalized 10 Gb/s data at the receiving end of a six inch FR4 PC board channel                                                                                                                                                         | 88  |

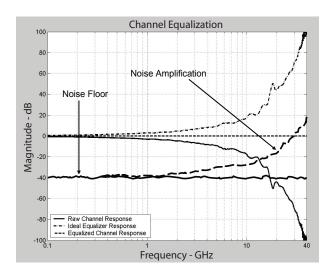

| 5.3  | Illustration of the basic channel equalization concept                                                                                                                                                                                                                         | 90  |

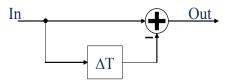

| 5.4  | "Delay and Subtract" discrete-time channel equalizer, which differentiates the passing signal, identifying signal transitions                                                                                                                                                  | 96  |

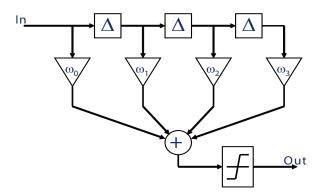

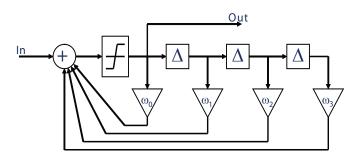

| 5.5  | Block diagram of a 4-tap finite impulse response or transversal filter.                                                                                                                                                                                                        | 96  |

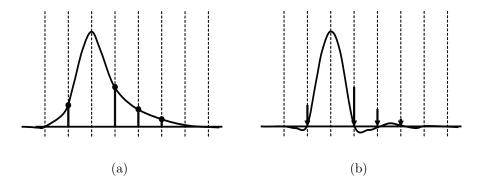

| 5.6  | Effect of discrete-time equalization on degraded pulse response. (a) Unequalized. (b) Equalized                                                                                                                                                                                | 97  |

| 5.7  | Block diagram of a 4-tap decision feedback equalizer                                                                                                                                                                                                                           | 97  |

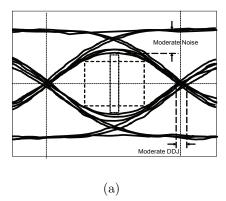

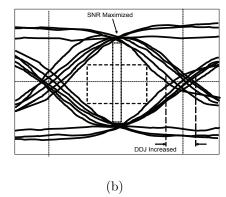

| 5.8  | Eye diagrams used to illustrate the simultaneous impact of discrete-time equalization on SNR and jitter, and the sensitivity of discrete-time equalized signals to sampling uncertainty                                                                                        | 99  |

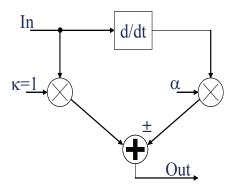

| 5.9  | The continuous-time magnetic read channel equalizer                                                                                                                                                                                                                            | 100 |

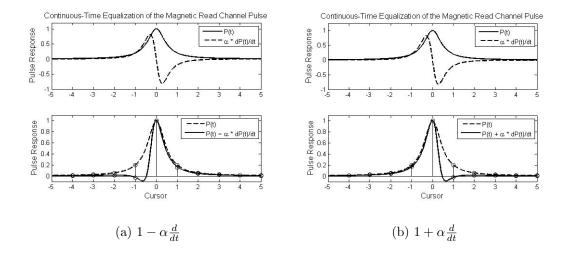

| 5.10 | Application of the $1\pm\alpha\frac{d}{dt}$ equalizer to the magnetic read channel pulse.<br>(a) Pre-cursor Equalization. (b) Post-cursor Equalization                                                                                                                         | 101 |

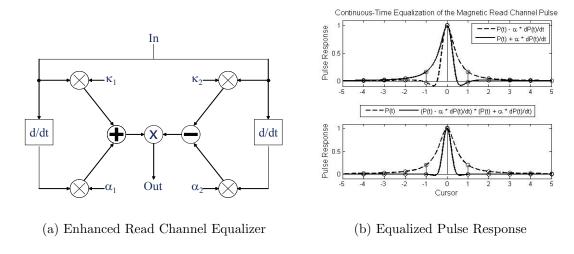

| 5.11 | (a) Enhanced magnetic read channel equalizer topology for canceling both pre and post-cursor ISI. (b) Application of the pre/post cursor equalizer to the magnetic read channel pulse                                                                                          | 102 |

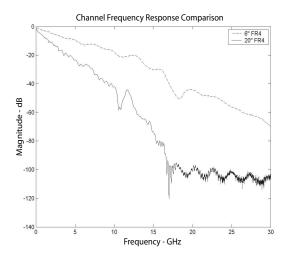

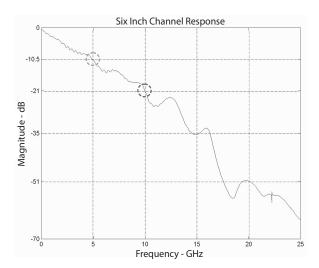

| 6.1  | Channel frequency responses for the target six inch and twenty inch copper traces across an FR4 PC board                                                                                                                                                                       | 109 |

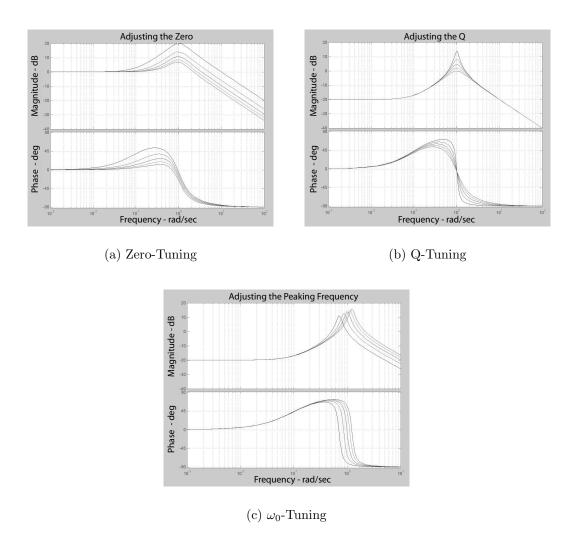

| 6.2  | Comparison of equalization through adjusting (a) the zero (b) the Q (c) the peak frequency $(\omega_0)$                                                                                                                                                                        | 110 |

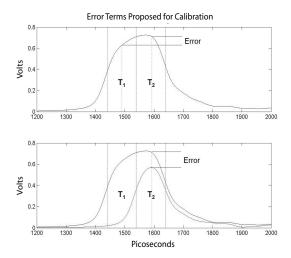

| 6.3  | New error terms proposed for filter coefficient calibration                                                                                                                                                                                                                    | 114 |

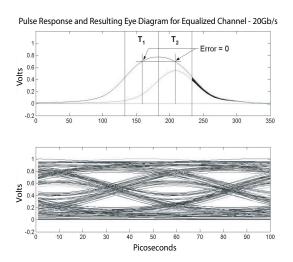

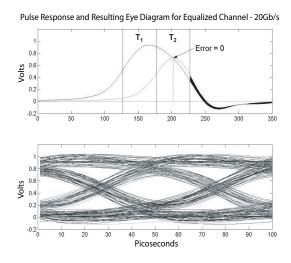

| 6.4  | The upper window presents the 20 Gb/s single and double pulse responses of the six inch FR4 channel after applying the <i>symmetric pulse</i> tuning algorithm. The lower window presents the resulting 20 Gb/s eye diagram                                               | 115 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

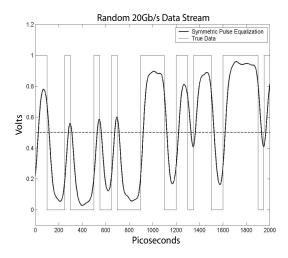

| 6.5  | Comparison of the transmitted data and the received data after <i>symmetric pulse</i> equalization                                                                                                                                                                        | 116 |

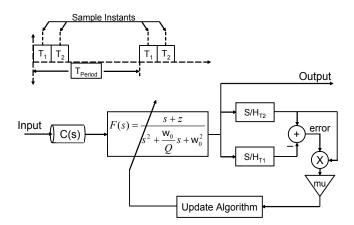

| 6.6  | Block diagram of the <i>symmetric pulse</i> tuning algorithm                                                                                                                                                                                                              | 117 |

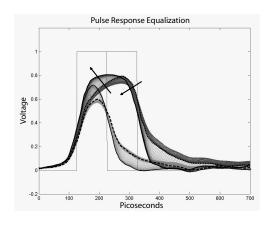

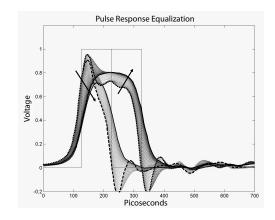

| 6.7  | Effect of <i>symmetric pulse</i> calibration on the single and double pulse responses. (a) Starting from an overdamped condition. (b) Starting from an underdamped condition                                                                                              | 118 |

| 6.8  | The upper window presents the 20 Gb/s single and double pulse responses of the six inch FR4 channel after applying the <i>reduced tail</i> tuning algorithm. The lower window presents the resulting 20 Gb/s eye diagram                                                  | 120 |

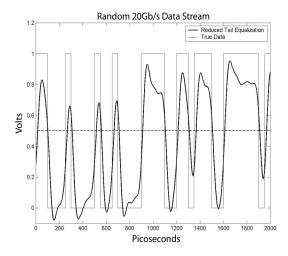

| 6.9  | Comparison of the transmitted data and the received data after $reduced$ $tail$ equalization                                                                                                                                                                              | 122 |

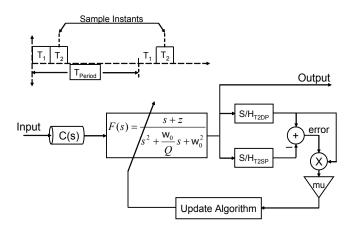

| 6.10 | Block diagram of the <i>reduced tail</i> tuning algorithm                                                                                                                                                                                                                 | 123 |

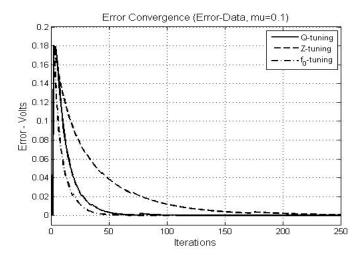

| 6.11 | Error minimization achieved through the variation of each of the three equalizer parameters                                                                                                                                                                               | 124 |

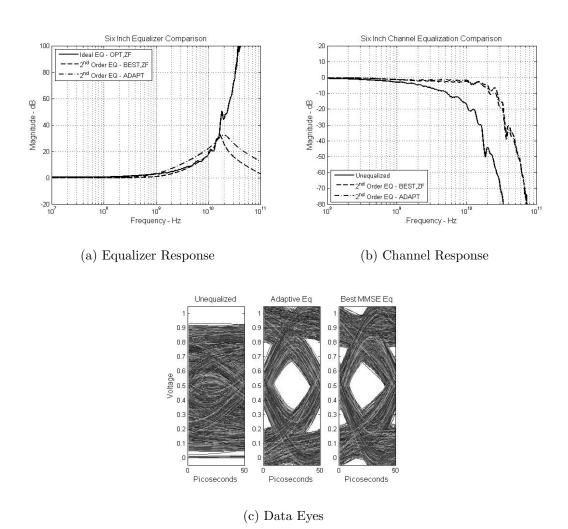

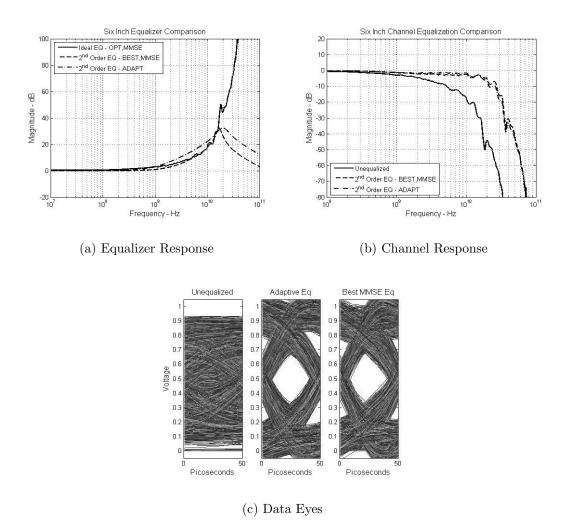

| 6.12 | Zero-forcing equalization comparison: six inch - $20~\mathrm{Gb/s}$ interconnect.                                                                                                                                                                                         | 127 |

| 6.13 | Zero-forcing equalization comparison: twenty inch - 10 Gb/s interconnect                                                                                                                                                                                                  | 128 |

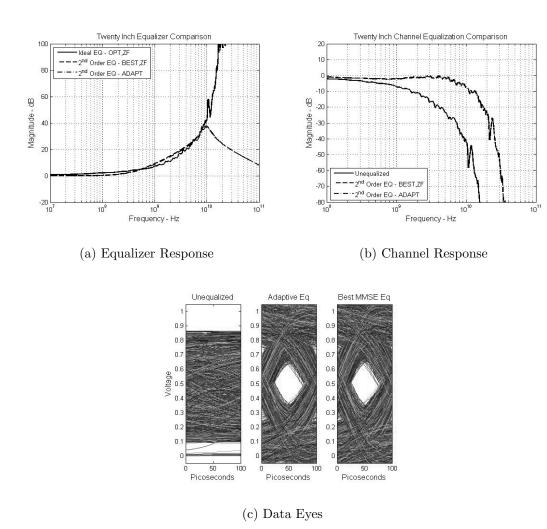

| 6.14 | MMSE equalization comparison: six inch - 20 Gb/s interconnect. $$                                                                                                                                                                                                         | 130 |

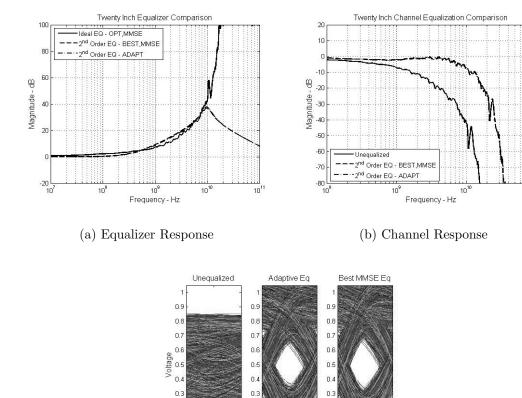

| 6.15 | MMSE equalization comparison: twenty inch - 10 Gb/s interconnect.                                                                                                                                                                                                         | 131 |

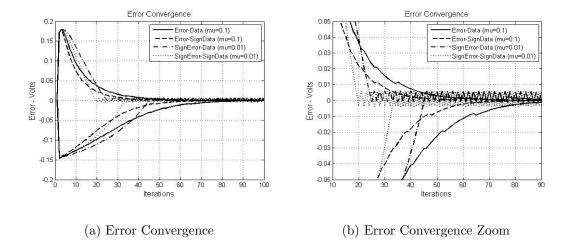

| 6.16 | Simulations tracking the coefficient adaptation from both overdamped and underdamped initial conditions, when driven by the LMS, sign, signed-regressor, and sign-sign algorithms. (a) Zoomed out to show relative convergence time. (b) Zoomed in to show residual error | 132 |

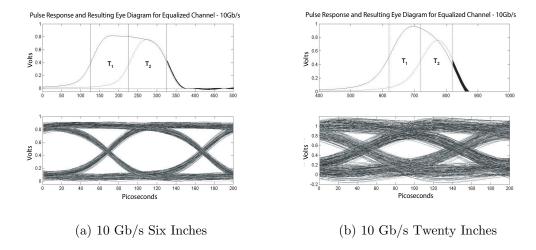

| 6.17 | (a) Pulse response and resulting eye diagram for a 10 Gb/s data stream (a) transmitted across the six inch channel (b) transmitted across the twenty inch channel                                                                                                         | 134 |

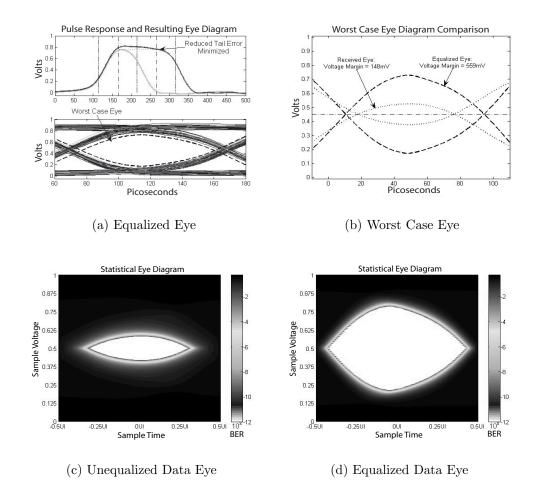

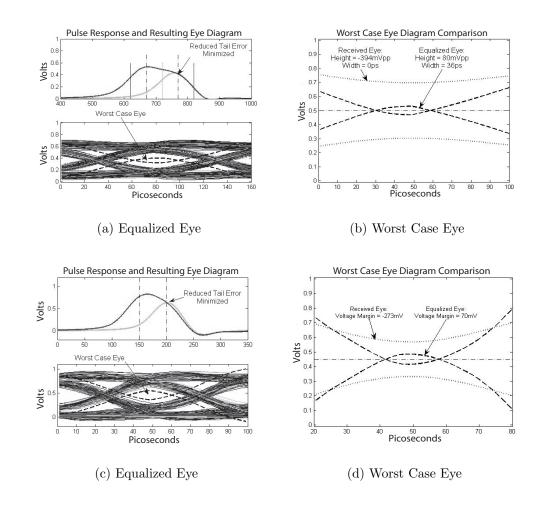

| 6.18 | Various illustrations of the impact of the <i>reduced tail</i> calibrated equalizer on the six inch channel at 10 Gb/s. (a) Single and double pulse responses and resulting eye diagram. (b) Worst case unequalized and equalized inner eye boundaries. (c) Unequalized statistical data eye. (d) Equalized statistical data eye.    | 135 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

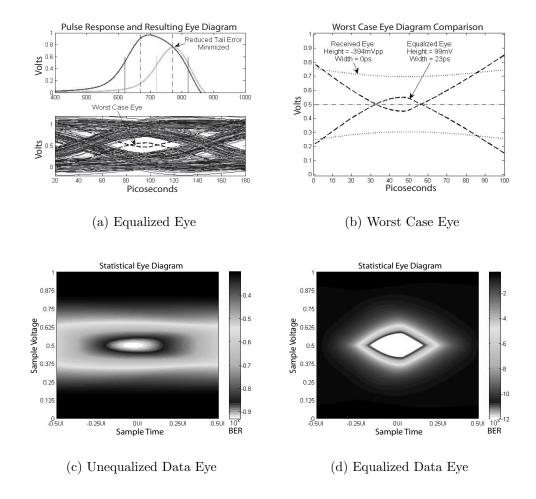

| 6.19 | Various illustrations of the impact of the <i>reduced tail</i> calibrated equalizer on the twenty inch channel at 10 Gb/s. (a) Single and double pulse responses and resulting eye diagram. (b) Worst case unequalized and equalized inner eye boundaries. (c) Unequalized statistical data eye. (d) Equalized statistical data eye. | 136 |

| 6.20 | (a)-(b) Impact of the <i>reduced tail</i> calibrated equalizer on the twenty inch channel at 10 Gb/s. In this case, the frequency zero in the equalizer transfer function is initial set 3x higher than in Fig 6.19. (c)-(d) impact of the <i>reduced tail</i> calibrated equalizer on the six inch channel at 20 Gb/s               | 137 |

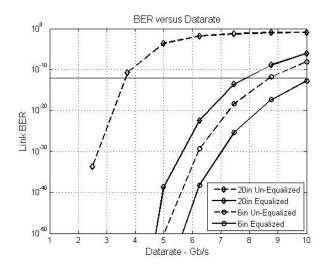

| 6.21 | BER versus datarate for the six inch and twenty inch channels before and after equalization                                                                                                                                                                                                                                          | 138 |

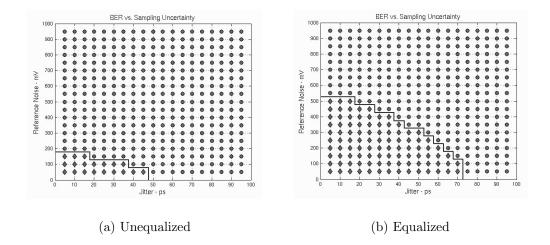

| 6.22 | Tolerable sampling uncertainty levels in terms of sampling jitter and reference voltage noise. (a) Unequalized. (b) Equalized                                                                                                                                                                                                        | 139 |

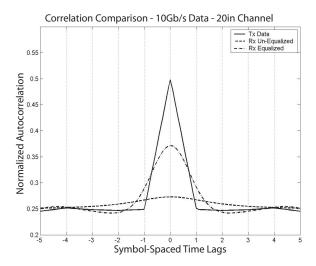

| 6.23 | Comparison of the calculated autocorrelations of the transmitted, received, and equalized data sets                                                                                                                                                                                                                                  | 141 |

| 6.24 | Equalizer with tunable inductive peaking.                                                                                                                                                                                                                                                                                            | 142 |

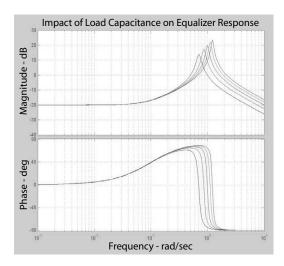

| 6.25 | Frequency response of the suggested equalizer for various levels of tuned load capacitance                                                                                                                                                                                                                                           | 143 |

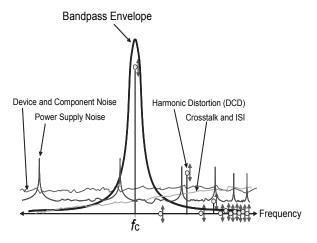

| 7.1  | High-level frequency domain illustration of the impact that a bandpass filter should have on the spectral components of clock degrading noise.                                                                                                                                                                                       | 147 |

| 7.2  | Target clock channel frequency response for a six inch FR4-based printed circuit board interconnect                                                                                                                                                                                                                                  | 149 |

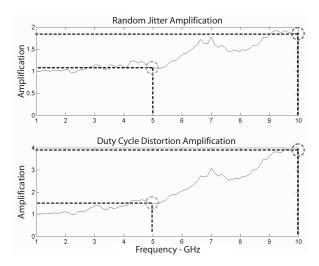

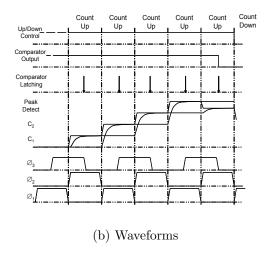

| 7.3  | Anticipated RJ and DCD amplification at various clock frequencies for a six inch FR4-based printed circuit board interconnect                                                                                                                                                                                                        | 150 |

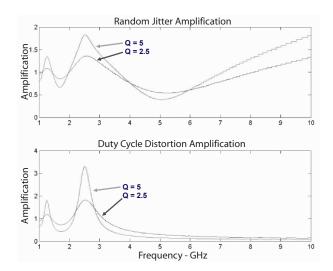

| 7.4  | Anticipated RJ and DCD amplification for two bandpass filters with Qs of 2.5 and 5                                                                                                                                                                                                                                                   | 151 |

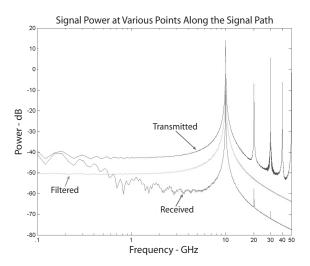

| 7.5  | Power spectral densities at the transmitter, the receiver and following the bandpass filter                                                                                                                                                                                                                                          | 152 |

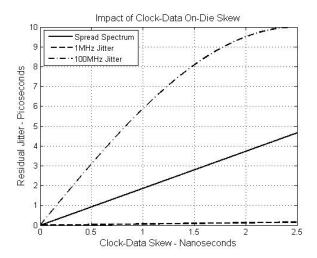

| 7.6  | Residual sinusoidal jitter components that may result from on-chip clock and data routing mismatch                                                                                                                                                                                                                                   | 154 |

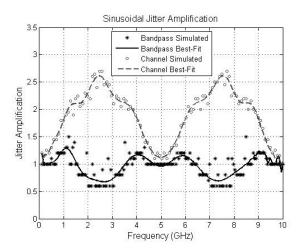

| 7.7  | Sinusoidal jitter amplification of the proposed bandpass filter with clock frequency fixed at 5 GHz and sinusoidal jitter frequency swept from 100 MHz to 10 GHz                                                                                                                                                | 155 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

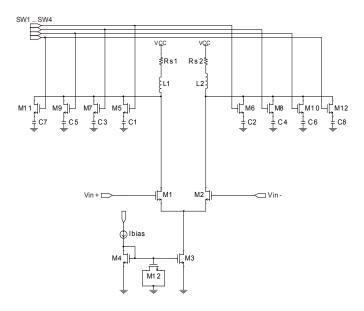

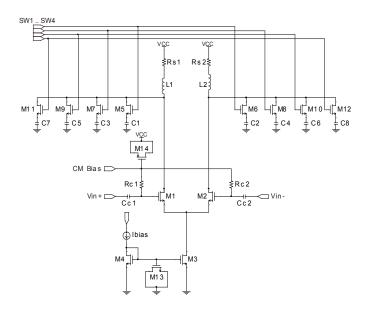

| 7.8  | Schematic of the proposed bandpass filter                                                                                                                                                                                                                                                                       | 159 |

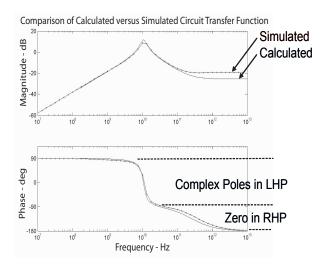

| 7.9  | Comparison of the bandpass filter's frequency response with the expression found in (7.3)                                                                                                                                                                                                                       | 162 |

| 7.10 | 4-bit tuning range of the proposed bandpass filter                                                                                                                                                                                                                                                              | 163 |

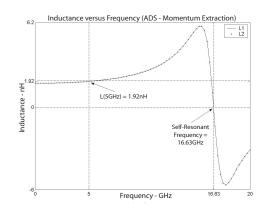

| 7.11 | Micro-photograph and simulated impedance response of the on-chip spiral inductors                                                                                                                                                                                                                               | 164 |

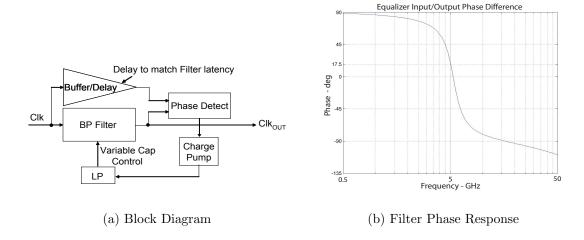

| 7.12 | Phase Tuning: (a) Block diagram of a center frequency tuning scheme based on phase-locking. (b) Simulated filter phase response identifying the residual phase offset at the center frequency due to the signal propagation delay through the filter circuitry and the impact of the inductor's series resistor | 168 |

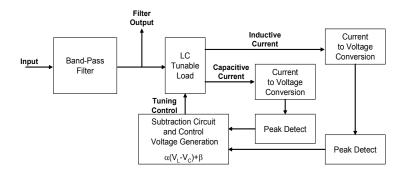

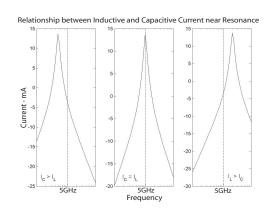

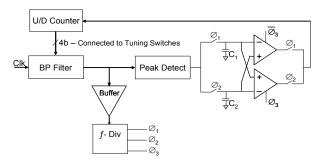

| 7.13 | LC Tuning: (a) Block diagram of a center frequency tuning scheme based on inductive/capacitive current comparison. (b) Waveforms corresponding to the calibration algorithm.                                                                                                                                    | 169 |

| 7.14 | Peak Tuning: (a) Block diagram of a center frequency tuning scheme based on peak detection. (b) Waveforms corresponding to the calibration algorithm                                                                                                                                                            | 171 |

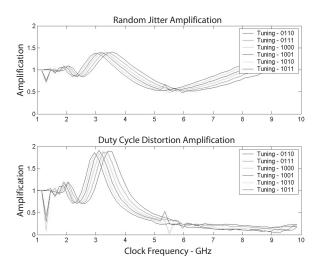

| 7.15 | Simulated jitter amplification versus filter center frequency tuning                                                                                                                                                                                                                                            | 173 |

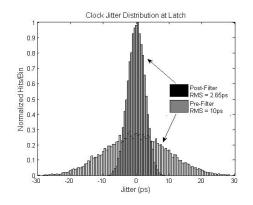

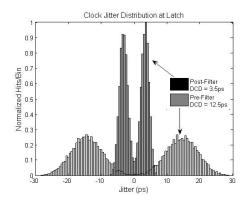

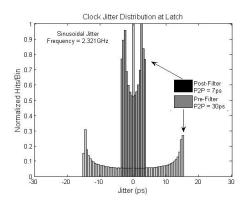

| 7.16 | Simulated impact of the proposed bandpass filter on clock jitter components. (a) Gaussian distributed RJ. (b) DCD. (c) Sinusoidal jitter.                                                                                                                                                                       | 174 |

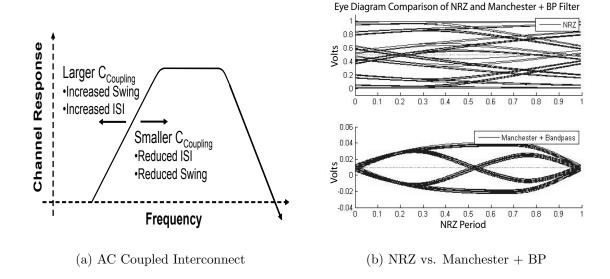

| 8.1  | (a) Impact of narrowband filtering broadband data signals. (b) Simulated eye diagrams of band-limited NRZ data and Manchester encoded data followed by a bandpass filter                                                                                                                                        | 182 |

### Chapter 1

#### Introduction

As datarates approach and surpass multi-Gigabit/second (Gb/s) levels, the challenge of maintaining signal integrity across chip-to-chip interconnects grows due to the introduction of several analog phenomena which impact digital signals in the Gigahertz (GHz) frequency range. Fortunately, many of the parasitic effects of the inter-chip channel are not new and neither is the demand for performance and bandwidth. Over the past century several communication media ranging from the telegraph to fiber optics have been explored and employed to meet the requirements of society. In every case bandwidth limitations have been overcome, or at least mitigated, through the ingenuity of communication engineers, and it is through the leveraging of proven signal conditioning techniques that datarates have achieved their current levels.

Today the push toward ever higher operating speeds in consumer electronics is driven, in part, by growing software complexity. To maintain a given level of perceived performance, added complexity in the underlying software must be balanced or tracked by improvements in processing efficiency. That processing efficiency is not only a function of the clock frequency of the micro-processor unit (MPU), but is also highly dependent upon the available system memory and the rate at which the MPU, memory, and other peripheral components communicate.

One popular prediction of the anticipated growth in software complexity is attributed to Sun Microsystems' Greg Papadopoulos who stated that "the mass and volume of software, (i.e. LOC size<sup>1</sup>, memory demands, and processor loading) increase

$<sup>^{1}</sup>LOC = Lines of Code$

in an inverse natural logarithm relationship to the available processor resources," which, according to Moore's Law is anticipated to double every two years [1].

Figure 1.1: Trends in computing speed supply and demand.

In other words, even as MPU operating speeds and computational efficiency increase, the sheer complexity and mass of the associated software obscure much of the performance enhancement obtained at higher clock frequencies. Fig. 1.1 provides a visual comparison of Moore's Law and Greg's Law, clearly identifying the gap between the demand for increased computational power and the achieved growth in computational resources. High definition television, multi-Megapixel digital cameras, music and image file-sharing, as well as the rapid growth in the complexity and detail of graphics emerging from the \$30 billion electronic gaming industry [2] are just a few examples of the growing computational load imposed on today's MPU.

To accommodate the market's insatiable appetite for bandwidth, MPUs are forced to share their computational burden with other application specific chips, including memory controllers, graphics processors, etc. Unfortunately the inter-chip

communication link has historically been the limiting factor or bottleneck in overall system performance [3], because while circuits on a single chip are capable of communicating at incredible speeds, communication between circuits located on separate chips is severely impeded by signal-degrading effects inherent in the chip-to-chip signal path. The third curve in Fig. 1.1 verifies this, as it tracks the growth in memory bus bandwidth over the corresponding time period. If Greg's Law may be considered a representation of the demand for inter-chip communication, then there is a terrible discrepancy between the demand for and the achieved inter-chip bandwidth.

Yet, obstacles facing digital communication engineers are not limited to the derivation of signal conditioning circuitry to counter the impact of limited channel bandwidth, but also include the task of developing models and methodologies suitable for capturing and characterizing the newly encountered signal degradation as well as for analyzing and verifying proposed signal conditioning solutions. The cost of initial development and design prototyping has grown so great that the methodology of design iteration is no longer acceptable; rather, designs must function with the first pass. Failing to emulate the true operating conditions, including signal integrity, guarantees failure at multi-Gb/s rates. Conversely, when circuits are exercised in the presence of realistic degradation, success in simulation becomes a better predictor of success within the system.

The challenge associated with simulating channel-affected signals is highly correlated to the characteristics of the degradation. As will be discussed in greater detail, signals in any transmission medium experience both random and deterministic degradation. Random degradation, in the form of random Gaussian distributed voltage noise and timing noise or jitter stemming from several sources, requires statistical quantification. Similarly, deterministic voltage noise and jitter linked to power supply noise, inter-channel crosstalk, impedance discontinuities, component variance, and at high frequencies the response of the channel, result in a variety of observable characteristics, from periodicity to uncorrelated-bounded randomness. To model these noise components correctly requires the ability to designate their probability during the noise generation stage and consequently inject or superimpose these effects onto

the underlying signals and power supplies in a way reflecting what occurs in the actual system.

To date, industry standard simulators do not provide the level of noise and jitter generation control needed to accurately model a realistic communication link. While some of the more advanced, and hence expensive, tools provide for an accurate generation of Gaussian distributed noise and jitter, no simulator in existence allows for the derivation of signals exhibiting the random, periodic, and aperiodic jitter encountered in the real world. <sup>2</sup>

A second challenge in simulating realistic signaling environments is tied to the underlying statistical assumption that a sufficient number of samples of the behavior to be characterized are available. As such, it is becoming necessary to include more and more cycles with each simulation. At the same time, the relative size of each individual noise and jitter component is very small with respect to the overall signal swing and symbol period or unit interval (UI), implying that fine voltage and timing resolution are also necessary. When fine simulated resolution is coupled with a greater number of simulated cycles, the result is an enormous amount of data and prohibitively lengthy simulation times. It is not uncommon for transistor-level transient (time-based) simulations to run for hours or even days. It is also not uncommon for such simulations to fail after several hours due to a lack of memory resources. And in some circumstances, these incredibly long simulations finish successfully, yet the results are not viewable due to the enormous amount of data output by the simulator and the limited capacity of industry standard waveform viewers.

To speed design-to-market time, the growing trend is to compartmentalize system circuitry during the verification process. Rather than simulate the full system at the transistor level, smaller circuit blocks are characterized in Spice-based simulators and then those characteristics are used to construct behavioral models that may be included in simulations at higher levels of abstraction [5]. This methodology is

<sup>&</sup>lt;sup>2</sup>Agilent Technology's Advanced Design System (ADS) provides a square-wave clock with Gaussian distributed random jitter for transient simulation. This jittery clock source may also be used to trigger a random data source, thereby adding random jitter to the data signal. While the simulated jitter closely approximates a true Gaussian distribution, other jitter components commonly encountered in fabricated circuits are not directly realizable in ADS (periodic jitter, etc.) [4].

very effective when implemented carefully, but has the potential for providing unrealistic performance predictions, as much of the nonlinear circuit behaviors are lost in the translation from transistor-based circuits to behavioral circuits.

In addition to breaking the system down into more manageable blocks, it is not uncommon for voltage and timing noise to be evaluated independently. One of the weaknesses in this approach is that it fails to capture the interaction of voltage noise and timing jitter. As will be shown, voltage and timing noise exhibit a synergistic relationship, wherein each leads to the other and together they combine to limit performance wherever they are encountered.

In this dissertation both the need for enhanced signal conditioning circuitry and the need for improved verification methodologies are addressed. The main contributions of this work to the prior art include:

- 1. The development of a signal modeling methodology based on Fourier theory which allows for the generation of both periodic clock and random data signals with nearly unconstrained, yet completely controllable, voltage and timing noise characteristics. Because the techniques derive true signals, with both voltage and timing dimensions, the full interaction of voltage and timing noise may be simulated leading to new levels of realism during system verification and signal integrity analysis.<sup>3</sup>

- 2. The development of an alternative signal waveform generation technique which overcomes some of the limitations of the Fourier-based approach at the cost of some flexibility.

- 3. The development of self-calibration algorithms for continuous-time data channel equalization targeting the suppression of inter-symbol interference (ISI), the novelty of which is in the simplicity and effectiveness of the techniques, which take repeated samples of the channel's single pulse and double pulse responses

<sup>&</sup>lt;sup>3</sup>A patent application entitled "Generation and Manipulation of Signals for Circuit and System Verification," was filed on October 14, 2006. Two additional patents have been approved for filing covering the jitter phase control provided by the proposed signal generation technique and an extension of the technique to incorporate finite impulse response pre-filtering of the generated signals.

and tune the frequency response of the equalizer to effectively reduce ISI with only one degree of freedom. $^4$

4. The design and implementation of a fully differential 5 GHz bandpass filter with associated center frequency tuning circuitry for reducing clock jitter in source-synchronous serial communications.<sup>5</sup>

In the chapters that follow, more adequate motivation for the development of novel modeling and noise suppression techniques will be provided. Chapter 2 begins by presenting common high-speed electrical signaling topologies and goes on to describe the signal degradation common to such interconnects. It discusses the sources of degradation and then further separates the observable noise into voltage and time-domain components with their many sub-components. With the foundation provided in Chapter 2, Chapter 3 discusses many of the challenges associated with generating waveforms exhibiting realistic noise in a way suitable for and compatible with time-domain simulation. Chapter 3 also discusses the growing problem of simulator efficiency. Chapter 4 goes on to present a new method for generating jittery clock and data signals. In the case of the clock generation, the techniques proposed also facilitate efficient high-speed clock channel simulation. Chapter 5 goes on to discuss existing techniques for mitigating voltage and timing noise imposed by band-limited clock and data channels. Chapter 6 takes a continuous-time equalizer topology and presents new methods of self-calibration which tune the equalizer's frequency response using only one degree of freedom, based on one of two simple algorithms operating on the single pulse and double pulse responses of the channel. Chapter 7 presents a fully differential, LC-based, tunable bandpass filter designed to reduce both random and deterministic degradation of forwarded clock signals. And finally, Chapter 8 summarizes the contributions of this work and suggests paths for continued research in the areas presented.

<sup>&</sup>lt;sup>5</sup>A patent application covering the bandpass filter design and one of the center frequency tuning schemes was filed by the Intel Corporation on December 30, 2005, entitled "Forwarded Clock Filtering."

$<sup>^4\</sup>mathrm{A}$  patent is being being drafted presently by Micron Technology, Incorporated, covering facets of the proposed equalizer calibration algorithms.

### Chapter 2

## **High-Speed Interconnects - Topologies and Limitations**

Before discussing the several performance limiting phenomena encountered in the high-speed PC board-based communication link, it is helpful to become familiar with the standard link architectures.

#### 2.1 Common Interconnect Topologies

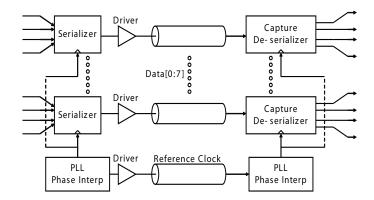

Today's high-speed chip-to-chip communication is dominated by two interconnect topologies, which are both shown in Fig. 2.1. The upper window presents a

high level diagram of the source-synchronous link, wherein a reference clock signal,

initially in "sync" or phase with the data, is forwarded to the receiver in parallel with

the data across a dedicated channel. At the receiving end, this clock, or one derived

from it, is used to sample the data waveform during the data detection and recovery

process. By routing the clock and data signal paths close together it is hoped that

system and environmental noise will impact both signals equivalently. In addition

to the close proximity of the clock and data signals, the respective paths are also

carefully matched, in terms of length, to insure that commonly experienced noise will

remain correlated and cancel out when the forwarded-clock is used to sample and capture the transmitted data. The lower window presents the clock-data-recovery (CDR)

architecture, wherein the clock is not forwarded along with the data, but rather is

encoded into the data and extracted prior to data detection within the receiver.

For several reasons, true source-synchronous operation is becoming more and more difficult to implement. First of all, the demand for increased aggregate inter-chip bandwidth has been met, in part, through an increase in parallelism or

Figure 2.1: Simplified diagrams of source-synchronous (top) and clock-data-recovery (bottom) interconnect topologies.

the number of chip-to-chip connections. As a result it is nearly impossible to match routing lengths identically when the simultaneous push to lower production cost limits the number of available PC board layers onto which the signal paths may be laid out. Incidentally, it is this challenge of route matching between chips that has steered signaling standards from the true parallel link to a set of parallel running serial links, as serial communication is less sensitive to propagation delay mismatch between parallel signals.

In addition to the required off-chip matched routing, there is often some degree of on-chip clock and data routing that must be matched just as carefully. This stems from the fact that many data signals are forced to share a common reference clock. Due to the growing cost of pins on the IC package, a single clock is often associated with 8-32 data lanes. When this occurs, the clock must be distributed across the receiving port, which introduces latency in the clock path and potentially de-correlates noise that was still common to the clock and data signals at the receiving end of the off-chip channel as the result of careful off-chip routing. In order to

guarantee that the clock and data signals arrive at the point of data capture simultaneously, it is thus necessary to extend on-chip data wiring to match the propagation delay incurred through the on-chip clock distribution network. The problem with this approach is not so much the complication of having to match clock and data paths, but rather the limited achievable bandwidth of input data buffers. The signal attenuation resulting from the channel, pin, and pad capacitance requires that signals be amplified before being routed any further on chip, but designing an input buffer to provide amplification at multi-GHz frequencies is nearly impossible in standard CMOS technology. Still, the Joint Electron Device Engineering Council or JEDEC has determined that this approach provides the best performance while still meeting area and power requirements, and in so doing incorporated the source-synchronous interconnect with data input buffering for on-chip matched routing into the specification of the most recent memory standard, DDR3, which is intended to operate up to 1.6 Gb/s [6].

To avoid the input buffer dilemma, a growing trend is to capture the data right at the pad, or right as it enters the chip. The difficulty with this technique is that it still requires that a centralized clock signal be distributed across the input port, and in so doing guarantees a path mismatch equal in length to that of the clock distribution network. This is typically resolved by introducing a delay-locked loop (DLL) or a phase-locked loop (PLL) into the clock path. The DLL or PLL is then used to compensate for the inherent path mismatch by realigning the timing of the clock and data signals at the point of data capture. While this topology is often referred to as source-synchronous, due to the forwarded-clock, it is more correct to refer to it as meso-synchronous, as the clock and data paths are not strictly matched. A more detailed analysis of meso-synchronous links will be treated in the next chapter.

As was mentioned, in the CDR system shown in the lower window of Fig. 2.1, the transmitted data is still launched onto the channel in the same way, triggered by the transmit clock, but in this case, the clock is not forwarded to the other chip. Rather, the clock is embedded into the data bitstream through encoding at the transmitter, and is extracted at the far end for use in the data recovery process.

By embedding the clock into the datastream, correlation between the two signals is guaranteed at the cost of added receive-side complexity. While CDR topologies are finding increased popularity within the realm of electrical signaling, they are more often encountered in optical systems where simply laying out a parallel trace for a forwarded-clock is not possible [7].

### 2.2 Signal Degradation

As datarates increase, chip-to-chip signaling grows more challenging. Even in the ideal case (e.g. no signal degradation), the decreasing cycle time or UI demands faster circuit operation. At some point, even an ideally received data symbol will become impossible to detect correctly when the available sampling window falls below the setup-and-hold time required by the receiver. Noise, or distortion, only exacerbates the issue. Interestingly, it was the inherent immunity of digital communication systems to noise that made them so attractive in the first place. But as lowpass channel filters and reshapes the sharp edges of high-speed digital signals, the struggle to overcome noise and salvage performance becomes an analog design problem.

Fortunately, analog signal conditioning techniques are fairly mature, as analog communication has always been more sensitive to noise. Yet implementation of theoretically derived noise mitigation schemes is often not straightforward and many techniques must be altered through innovation to be useful at the high datarates presently targeted. In addition, new (previously inconsequential) noise is emerging directly as a result of higher frequency operation.

And while some signal conditioning techniques may address multiple noise components, the distinct nature of the various noise sources commonly encountered in baseband digital communications demands individualized solutions if optimal noise suppression is to be obtained. Similarly, to realistically represent the variety of noise components encountered in the typical inter-chip channel environment, it is critical to account for several unique characteristics including correlation or non-correlation to the signal swing and frequency, statistical characteristics, spectral content, etc. Thus before any solutions may be developed, whether addressing noise suppression

or simply noise modeling, it is first necessary to be familiar with the characteristics of the specific degradation to be addressed.

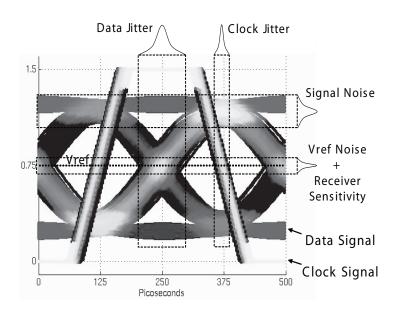

Noise, which in the broadest sense is manifested as deviations in the characteristics of a signal from ideal, must be considered in two dimensions: voltage noise or distortion along the vertical or amplitudinal axis and timing noise or jitter along the horizontal axis. Amplitudinal deviations in a given signal from ideal levels will be combined under the term voltage noise or simply noise through the remainder of this work. Similarly, deviations in the timing of significant signal events (e.g. transitions, etc.) from ideal are likewise lumped under the term timing noise or jitter. A common way to observe such cycle-to-cycle variation is through superimposing several consecutive cycles of simulated or measured waveforms to generate an eye diagram (see Fig. 2.2). Then by taking a vertical cross section of the eye at a specific point in time, the variations between the many levels at which the signal crosses that point in time are considered the voltage noise experienced over the captured cycles. Similarly, a horizontal cross section, typically taken at the level mid-way between the high and low binary levels of the signal identifies the signal jitter as the varied time points at which the transitioning signal passes through the threshold.

Figure 2.2: Example data eye diagram.

Both voltage noise and jitter are made up of several contributing factors, and as will be shown later, while noise and jitter may be injected into the signal independently, by the time the signal has passed through the next system block in the communication link, the noise and jitter exhibit a strong correlation. Over the next several pages, both noise and jitter will be decomposed and the sources of the individual components will be identified.

### 2.2.1 Voltage Noise

Voltage noise sources may be separated into two categories: proportional noise sources and fixed noise sources. Proportional noise sources exhibit a dependence on the signal swing while fixed noise sources are considered independent of the signal. To understand the implications of this statement it is necessary to introduce the term signal-to-noise ratio (SNR). SNR quantifies the ratio of the signal power to the observed noise power. Not only does it provide an intuitive description of the quality of a given communication link, but it can be used directly to predict both the achievable bit-error-rate (BER), or the number of bits that may be transmitted error-free, and capacity of the link when the channel bandwidth is known [8, 9]

To calculate the SNR of a particular link, it is first necessary to identify all of the contributing noise sources and separate them into the two categories just mentioned. Then by following the procedure found in [8], the SNR and corresponding BER may be computed. First, a value representing the total independent or random noise  $V_N$  is computed through combining the rms levels of all uncorrelated noise sources through the expression:

$$V_N = \sqrt{\sum_i V_{Ni}^2} \tag{2.1}$$

where  $V_{Ni}^2$  is the variance of the i<sup>th</sup> contributing source. The next step is to compute the signal power. For the purposes of calculating the BER, it is useful to let the signal value include all deterministic noise sources. Thus the signal level is found as:

$$V_S = \frac{\Delta V}{2} - V_D \tag{2.2}$$

where  $\Delta V$  is the peak-to-peak signal swing and  $V_D$  is the peak bounded noise level. This value may be generated through the overly pessimistic summation of the peak-to-peak levels of all deterministic noise sources or through a more elegant technique referred to as "peak distortion analysis" [10, 11]. By combining (2.1) and (2.2), the expression:

$$VSNR = \frac{V_S}{V_N} \tag{2.3}$$

may be used to calculate the voltage SNR. When considering noise as the only source of signal degradation, the expression:

$$P_{error} = \exp\left(-\frac{VSNR^2}{2}\right) \tag{2.4}$$

may in turn be used to compute the probability of error. Then based on the known bandwidth of the channel, Shannon's Theorem [12, 13] predicts that the link capacity is found through:

$$C = BW \log_2 \left( 1 + SNR \right) \tag{2.5}$$

where BW equals the channel's 3 dB bandwidth and SNR is considered here in terms of power rather than voltage.

Based on these expressions, it is clear that the performance of a communication link is highly dependent on the SNR, both in terms of achievable BER and capacity. Thus when the noise power grows while the signal power remains constant, the link performance is expected to degrade. However, when the noise is independent of the signal characteristics, then the SNR may be improved by increasing the signal power or swing. Conversely, when the noise is proportional to the signal, then increasing signal power simultaneously increases the noise power and the SNR, in theory, remains constant or may even decrease.

Two of the more pervasive proportional noise sources common to high-speed digital links are crosstalk (both inductive and capacitive) and simultaneous switching output (SSO) noise. SSO noise corresponds to the coupling of noise between transmit drivers. This noise is not necessarily crosstalk, by the standard definition, but rather results from imperfect power distribution. Ideally an unlimited amount of current is available to the circuits on-chip through a zero-resistance, zero-inductance supply network. In reality, the available current is finite and the supply network exhibits low resistivity and low inductance at best. The result of these nonidealities is that when relatively high-power driver circuits draw current from the power distribution, the resulting spikes in current generate short term voltage drops across the finite resistance between supply-line nodes, resulting in reduced bias conditions for neighboring drivers.

While crosstalk and SSO noise significantly contribute to the degradation of high-speed links, they are not the emphasis of this work. They have, however, been covered extensively in the literature [14, 15, 16, 17]. In addition, while crosstalk is often suppressed through careful layout and routing techniques, special circuits have also been developed to reduce its impact on performance [14, 15, 9]. SSO noise has also been addressed, with most approaches based on modifying driver topologies to reduce slew-rates and high/sharp current draw from the supply [18, 19, 20]. SSO noise and crosstalk may also be reduced through special data encoding as well as a technique known as data bus inversion (DBI). DBI consists of inverting all or some of the parallel data bits prior to transmission in accordance with an algorithm determined to lower the potential noise. Such algorithms may be based on minimizing the number of parallel transitioning bits or may simply seek to reduce the number of transmitted ones or zeros for power conservation. In either case, an additional signal must be added to the bus to indicate that bus inversion has taken place. The additional cost of the DBI implementation and parallel interconnect must be weighed with the noise-suppressing ability of the technique.

<sup>&</sup>lt;sup>1</sup>An alternative DBI algorithm based on balancing the number of simultaneously transmitted ones and zeros across the bus has been approved for patent filing.

In addition to the proportional noise sources, the two most common noise components which exhibit little dependence on the signal swing are random noise and inter-symbol interference (ISI).

Random noise is the result of random effects such as the random thermal motion of electrons in resistors (thermal noise) or the random fluctuations in current due to the granularity of electron current flow (shot noise). Its random nature makes it easily approximated with a Gaussian probability density function (pdf). This type of noise has probably been studied more than any other. As such, it is only mentioned here, but a more comprehensive treatment is found in [21].

ISI is a phenomenon associated with both the transmission environment and the transmitted signal characteristics, though not signal power as just discussed. Strictly speaking, ISI is the result of overlapping transmitted symbols in the bitstream. This symbol overlap may be due to the close proximity of the symbols in time or it may simply be the overlapping of a forward going symbol with some residual signal reflection. The severity of the distortion is determined by the signal pattern and frequency.

The key to ISI and other deterministic signal degradation is that, by definition, it is predictable and potentially reversible. Three keys to mitigating deterministic degradation are the use of channel equalization techniques to compensate for high frequency losses (a focus of this thesis), better channel termination practices, and the minimization of discontinuities along the chip-to-chip signal path.

For the same reason that the number of routing layers on the board are limited, namely due to cost, the quality of the board material is also often sacrificed to increase the profit margin of the end product. As a result, almost all digital board-based communication is implemented across copper traces on FR4 (flame retardant) fiberglass PC boards. As will be shown, the combination of the copper trace and the FR4 medium imposes two forms of high frequency signal loss, which both attenuate the signal amplitude and spread the transmitted symbol energy in time. These two phenomena are known as the "skin effect" and dielectric loss. The bandwidth

constraints associated with these two effects are accounted for by the following two transfer function expressions, as presented in [9]. The first expressions:

$$H_{skin}(f) = e^{-(1+j) l\sqrt{\pi\mu\sigma f}}$$

(2.6)

describes the skin effect, or the crowding of current near the surface of the copper conductor at high frequencies. As the current moves out from the conductor's center to its edges, the current density decreases in the core of the conductor, and as a result the copper appears more resistive. According to the expression, this effect is proportional to the square root of the frequency f, the permeability  $\mu$ , and the conductivity  $\sigma$  of the conductor. Finally the impact of the skin effect grows more noticeable with the length of the transmission path, as referred to in the expression by the parameter l. The second expression:

$$H_{dielectric}(f) = e^{-l\sqrt{\epsilon_r} f/c \tan \delta}$$

(2.7)

refers to the frequency dependent losses associated with the dielectric properties of the board. In this case, the effect is again proportional to the length l of the channel, but now is also inversely proportional to the wavelength  $\lambda = c/f$  of the signal, where c corresponds to the speed of light and f is the signal frequency. And finally, the dielectric loss is proportional to the tangential loss factor of the material  $tan \delta$ . In addition, dielectric losses are also proportional to the square root of the dielectric constant  $\epsilon_r$ . While these two forms of signal loss are dependent on the physical makeup of the channel and medium (e.g., dielectric thickness, trace thickness and width, trace routing layer, etc.), the skin effect is consistently observed at lower frequencies (1-3 GHz), while above 3 GHz dielectric losses dominate the filtering of the signal.

A good source covering the impact of FR4 on signal integrity is found in [22]. This paper delineates the nonidealities of the PC board medium, discusses how the frequency dependent characteristics of the board impact both analog and digital signals, and then compares standard FR4 with many alternative and more expensive

board materials, in terms of the specific material parameters discussed. Unfortunately, the high cost of more signal friendly materials makes them unacceptable for high volume commodity production.

Interestingly, it is not the signal attenuation, resulting from the skin effect and dielectric losses, which pose the greatest challenge to high-speed digital signaling. Rather, it is nonuniform group delay that causes the greatest distortion. Group delay, defined as the derivative of the phase response of a system with respect to frequency, describes the relative propagation velocities of signals at distinct frequencies. Because the propagation time across the inter-chip channel is frequency dependent, and because digital signals are broadband by nature, spectral components of the transmitted digital pulse arrive at the receiving end of the channel at different times producing a smearing of the pulse, very different from the typical RC-filtered pulse response. This factor is not captured explicitly by equations (2.6) and (2.7), but rather is hidden within the not so constant dielectric constant  $\epsilon_r$ . As will be shown shortly, the pulse spreading that occurs in high frequency digital signaling can extend over several UI causing symbols to interfere with one another [23].

Figure 2.3: Illustration of the impact of ISI on signal amplitude and transition timing.